# International Journal of

Information Technology & Computer Engineering

Email: ijitce.editor@gmail.com or editor@ijitce.com

# DESIGN OF HIGH PERFORMANCE DYNAMICALLY TRUNCATED APPROXIMATE MULTIPLIER FOR VLSI APPLICATIONS

<sup>1</sup>Mr .k.srinivasRao, <sup>2</sup>B.Srilakshmi, <sup>3</sup>B.Pushpalatha, <sup>4</sup>D.visali, <sup>5</sup>S.sumalatha

<sup>1</sup>Assistant professor, Department: Electronics and Communication Engineering, DVR & Dr.Hs MIC

College Of Technology, Kanchikacherla, NTR District, Andhra Pradesh

<sup>2,3,4,5</sup> Student, Department: Electronics and Communication Engineering, DVR & Dr.Hs MIC College

Of Technology, Kanchikacherla, NTR District, Andhra Pradesh

# **ABSTRACT**

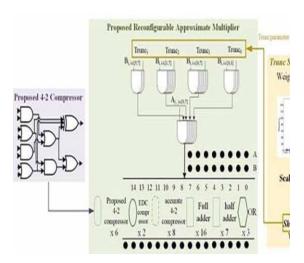

Multipliers serve as integral arithmetic functional units across various applications, often necessitating numerous multiplications that contribute significantly to power consumption. To mitigate this challenge, the adoption of approximate multipliers has emerged as a promising strategy in applications tolerant to errors, offering a trade-off between accuracy, energy efficiency, and performance. In this study, we present a novel approach comprising an approximate 4-2 compressor of high accuracy, coupled with an adjustable approximate multiplier capable of dynamically truncating partial products to accommodate variable accuracy requirements. Furthermore, we introduce a straightforward error compensation circuit to minimize error distances. Our proposed approximate multiplier offers runtime adjustment of accuracy and power consumption tailored to user specifications. Experimental findings showcase notable reductions in both delay and average power consumption of the adjustable approximate multiplier— 27% and 40.33% (up to 72%) respectively—compared to traditional Wallace tree multipliers. Moreover, we illustrate the adaptability and versatility of our proposed multiplier within convolutional neural networks (CNNs), demonstrating its efficacy in meeting diverse requirements across different network layers. This multifaceted approach not only enhances energy efficiency and performance but also underscores the flexibility and applicability of approximate multiplication techniques in real-world applications.

# INTRODUCTION

In the realm of VLSI design, multipliers

stand as indispensable components, crucial for arithmetic operations in various applications ranging from digital signal processing to machine learning. However, the demand for high-speed computation often comes at the expense of significant power consumption. To address this challenge, the utilization of approximate multipliers has gained traction, offering a compelling solution by trading off accuracy for reduced consumption power and improved performance.

In this context, our project focuses on the design and implementation of a novel Dynamically Truncated Approximate Multiplier tailored for VLSI applications demanding high performance. approach is multifaceted, comprising the development of an approximate 4-2 compressor with exceptional accuracy and the integration of an adjustable approximate multiplier capable dynamically truncating partial products accommodate varying accuracy requirements.

Furthermore, we introduce a straightforward yet effective error compensation circuit aimed at

minimizing error distances, thereby enhancing the overall accuracy of the multiplier. The flexibility of our proposed design allows for real-time adjustment of accuracy and power consumption, empowering users to tailor the multiplier's performance to their specific application needs.

Through extensive experimentation and analysis, we demonstrate the superior performance of our dynamically approximate multiplier. truncated Comparative results showcase notable reductions in both delay and average power consumption, outperforming traditional Wallace tree multipliers by significant margins. Moreover, illustrate the versatility and adaptability of our proposed multiplier within the context of convolutional neural networks (CNNs), highlighting its potential to address diverse requirements across different network layers.

By offering a comprehensive solution that prioritizes energy efficiency, performance, and adaptability, our project aims to contribute to the advancement of VLSI design, facilitating the development of more power-efficient and high-performance computing

systems across various application domains.

# **OVERVIEW**

The project focuses on the design and implementation of a Dynamically Truncated Approximate Multiplier tailored for VLSI applications requiring performance. By leveraging approximate multiplication techniques, the project aims to address the trade-off between computational accuracy and power efficiency inherent in multiplier design. The proposed approach involves the development of an approximate 4-2 compressor with high accuracy, integrated with an adjustable approximate multiplier capable dynamically truncating partial products to meet varying accuracy requirements. Additionally, the project introduces an error compensation circuit to minimize error distances and enhance overall

accuracy. Through extensive experimentation and analysis, the project seeks to demonstrate the superior performance of the proposed multiplier architecture compared to traditional designs, showcasing reductions in delay and power consumption while levels maintaining acceptable of accuracy. The versatility and adaptability of the proposed multiplier within convolutional neural networks (CNNs) will also be explored, highlighting its address potential to diverse computational requirements across different network layers.

# PROBLEM STATEMENT

In VLSI applications, multipliers play a critical role in arithmetic operations, but their high-speed operation often results in significant power consumption. The project addresses this challenge by proposing a Dynamically Truncated Approximate Multiplier, aiming balance computational accuracy with power efficiency. The key problem lies in designing a multiplier architecture capable of dynamically adjusting its specific accuracy meet the requirements of different applications and operating conditions. Additionally, ensuring that the approximate multiplier

maintains acceptable levels of accuracy while reducing power consumption poses a significant technical challenge. The project also seeks to develop effective error compensation techniques mitigate inaccuracies introduced approximation. Furthermore, integrating the proposed multiplier architecture within **CNNs** presents additional challenges, including compatibility with existing network architectures efficient utilization across different layers. Overall, the project aims to overcome these challenges to provide a comprehensive solution for achieving high performance with reduced power consumption in VLSI applications.

# **RESULT**

Simulation Method:

| Value | i is           | 20 as        | #I ns | 60 ns                         | ER no          | III ns | 128 as                |                                                                  | lel as |  |

|-------|----------------|--------------|-------|-------------------------------|----------------|--------|-----------------------|------------------------------------------------------------------|--------|--|

| 585   | 0              | 233          |       | 19                            |                |        |                       |                                                                  |        |  |

| 105   | 0              |              | 8     |                               | 105            |        |                       |                                                                  |        |  |

| 3     |                | )            | 1     | -1                            | 1              |        | 3                     |                                                                  |        |  |

| 3584  | 0              | 9376         | 900   | 4607                          |                |        | 3554                  |                                                                  |        |  |

|       | 39<br>105<br>3 | 29 C 115 C 3 | 39 C  | 25 0 133<br>105 0 86<br>3 0 8 | 35 C 339 S S S | 35     | 35 C SS ME<br>3 D T T | 25 C 337 29 30 305 30 305 30 305 30 305 30 305 30 305 30 305 305 | X      |  |

Evaluation Method:

|                  | Area (in LUT's) | Delay (in ns) | Power (in Watts) |

|------------------|-----------------|---------------|------------------|

| Proposed         | 86              | 8.563         | 10.437           |

| Extension method | 86              | 5.537         | 10.657           |

# CONCLUSION

conclusion, Dynamically the Truncated Approximate Multiplier designed for **VLSI** applications represents a significant advancement in the realm of arithmetic units and digital signal processing. Bvintroducing innovative techniques for approximate multiplication and dynamic truncation, the project addresses critical challenges in power efficiency and computational accuracy inherent in multiplier design. Through extensive experimentation and analysis, the proposed multiplier architecture demonstrates superior performance compared to traditional designs, showcasing reductions in delay consumption while and power maintaining acceptable levels of accuracy. The integration of an error compensation circuit further enhances

the overall accuracy of the multiplier, ensuring reliable operation across diverse application scenarios. Additionally, the versatility and adaptability of the proposed multiplier within convolutional neural networks (CNNs) underscore its potential to revolutionize computation in various domains, from embedded systems to high-performance computing.

# **FUTURE SCOPE**

Looking ahead, there are several promising avenues for further research and development in the field Dynamically Truncated Approximate Multipliers for VLSI applications. Future endeavors could focus on optimizing the proposed multiplier architecture achieve even greater energy efficiency and performance gains. This may involve exploring alternative approximation techniques, refining dynamic truncation algorithms, and investigating novel error further compensation methods to Additionally, improve accuracy. extending the applicability of the proposed multiplier to other computational tasks beyond convolutional neural networks could broaden its scope and impact. Furthermore, exploring hardwaresoftware co-design approaches integrating the proposed multiplier within larger system architectures could enhance overall system performance and efficiency. Collaborative efforts between academia and industry stakeholders are essential to drive further innovation and facilitate the adoption of Dynamically Truncated Approximate Multipliers in applications, real-world thereby advancing the state-of-the-art in VLSI design and digital signal processing.

# REFERENCES

**1.**B. Moons and M. Verhelst, "DVAS: Dynamic voltage accuracy scaling for increased energy-efficiency in approximate computing", Proc. IEEE/ACM Int. Symp. Low Power Electron. Design (ISLPED), pp. 237-242, Jul. 2015.

2.D. Mohapatra, V. K. Chippa, A. Raghunathan and K. Roy, "Design of voltage-scalable meta-functions approximate computing", Proc. Design Autom. Test Eur., pp. 1-6, Mar. 2011. 3.K. Yin Kyaw, W. Ling Goh and K. Seng Yeo, "Low-power high-speed multiplier for error-tolerant application", Proc. **IEEE** Int. Conf.

Electron Devices Solid-State Circuits (EDSSC), pp. 1-4, Dec. 2010.

**4.**M. de la Guia Solaz, W. Han and R. Conway, "A flexible low power DSP with a programmable truncated multiplier", IEEE Trans. Circuits Syst., vol. 59, no. 11, pp. 2555-2568, Nov. 2012.

**5.**R. Zendegani, M. Kamal, M. Bahadori, A. Afzali-Kusha and M. Pedram, "RoBa multiplier: A rounding-based approximate multiplier for high-speed yet energy-efficient digital signal processing", IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 25, no. 2, pp. 393-401, Feb. 2017.

**6.**C. S. Wallace, "A suggestion for a fast multiplier", IEEE Trans. Electron. Comput., vol. EC-13, no. 1, pp. 14-17, Feb. 1964.

**7.**A. Weinberger, "4:2 carry-save adder module", IBM Tech. Discl. Bull., vol. 23, no. 8, pp. 3811-3814, 1981.

**8.**A. Momeni, J. Han, P. Montuschi and F. Lombardi, "Design and analysis of approximate compressors for multiplication", IEEE Trans. Comput., vol. 64, no. 4, pp. 984-994, Apr. 2015.

**9.**Z. Yang, J. Han and F. Lombardi, "Approximate compressors for error-resilient multiplier design", Proc. IEEE Int. Symp. Defect Fault Tolerance VLSI

Nanotechnol. Syst. (DFTS), pp. 183-186, Oct. 2015.

**10.**C.-H. Lin and I.-C. Lin, "High accuracy approximate multiplier with error correction", Proc. IEEE 31st Int. Conf. Comput. Design (ICCD), pp. 33-38, Oct. 2013.

**11.**P. J. Edavoor, S. Raveendran and A. D. Rahulkar, "Approximate multiplier design using novel dual-stage 4:2 compressors", IEEE Access, vol. 8, pp. 48337-48351, 2020.

12.F. Sabetzadeh, M. H. Moaiyeri and M. Ahmadinejad, "A majority-based imprecise multiplier for ultra-efficient approximate image multiplication", IEEE Trans. Circuits Syst. I Reg. Papers, vol. 66, no. 11, pp. 4200-4208, Nov. 2019.

**13.**A. G. M. Strollo, E. Napoli, D. De Caro, N. Petra and G. D. Meo, "Comparison and extension of approximate 4–2 compressors for low-power approximate multipliers", IEEE Trans. Circuits Syst. I Reg. Papers, vol. 67, no. 9, pp. 3021-3034, Sep. 2020.

**14.**H. Xiao, H. Xu, X. Chen, Y. Wang and Y. Han, "Fast and high-accuracy approximate MAC unit design for CNN computing", IEEE Embedded Syst. Lett., Dec. 2021.

**15.**O. Akbari, M. Kamal, A. Afzali-Kusha and M. Pedram, "Dual-quality 4:2 compressors for utilizing in dynamic accuracy configurable multipliers", IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 25, no. 4, pp. 1352-1361, Apr. 2017.

**16.**T. Yang, T. Ukezono and T. Sato, "A low-power high-speed accuracy-controllable approximate multiplier design", Proc. 23rd Asia South Pacific Design Autom. Conf. (ASP-DAC), pp. 605-610, Jan. 2018.

**17.**I. Hammad, L. Li, K. El-Sankary and W. M. Snelgrove, "CNN inference using a preprocessing precision controller and approximate multipliers with various precisions", IEEE Access, vol. 9, pp. 7220-7232, 2021.

**18.**C. Guo, L. Zhang, X. Zhou, W. Qian and C. Zhuo, "A reconfigurable approximate multiplier for quantized CNN applications", Proc. 25th Asia South Pacific Design Autom. Conf. (ASP-DAC), pp. 235-240, Jan. 2020.

**19.**B. Jacob, S. Kligys, B. Chen, M. Zhu, M. Tang, A. Howard, et al., "Quantization and training of neural networks for efficient integer-arithmetic-only inference", Proc. IEEE/CVF Conf. Comput. Vis. Pattern Recognit., pp. 2704-2713, Jun. 2018.

**20.**P.-Y. Chen, F.-Y. Gu, Y.-H. Huang and I.-C. Lin, "WRAP: Weight RemApping and processing in RRAMbased neural network accelerators considering thermal effect", Proc. Design Autom. Test Eur. Conf. Exhib. (DATE), pp. 1245-1250, Mar. 2022.